## Dai circuiti combinatori alle reti sequenziali: i FLIP FLOP

Nei circuiti combinatori le uscite dipendono, in un determinato istante, unicamente dai valori assunti dagli ingressi nello stesso istante, ed inoltre il ripetersi di una eguale configurazione di ingresso produce necessariamente la medesima risposta delle uscite, senza tener conto delle precedenti situazioni.

Nell'elettronica digitale è spesso necessario disporre di sistemi logici variamente complessi, che chiameremo *reti sequenziali*, in grado di fornire una o più uscite dipendenti sia dagli stati logici attuali che da quelli precedenti acquisiti dagli ingressi. Ciò comporta che il circuito ricordi lo *stato precedente*, che deve quindi essere stato registrato e mantenuto. Da questo derivano due aspetti essenziali:

- una rete sequenziale è anche un *circuito di memoria*;

- la configurazione assunta dalle uscite dovrà essere determinata non solo dalla configurazione degli ingressi, come in un semplice circuito combinatorio, ma anche dall'informazione dello stato precedente, che il circuito stesso ha memorizzato e trattenuto in uscita. Ne consegue che i circuiti sequenziali dovranno essere provvisti di rete di retroazione per trasferire in ingresso tale informazione; si tratta di circuiti ad *anello chiuso*.

I flip-flop sono dispositivi sequenziali in grado di memorizzare un bit. Vi sono vari tipi di flip-flop che differiscono, sostanzialmente, per il diverso meccanismo di memorizzazione del bit. Gli ingressi dei flip-flop possono essere distinti in *sincroni* e *asincroni*:

- *sincroni* sono gli ingressi la cui influenza sullo stato delle uscite è subordinata alla presenza di un segnale esterno di sincronismo, *clock (CK)*; tale segnale è generalmente periodico e deve essere molto stabile, poiché da esso dipendono le fasi di funzionamento del FF;

- *asincroni* sono gli ingressi la cui influenza sullo stato delle uscite non dipende da alcun segnale di sincronismo. Rientrano in questo tipo di segnali i comandi di:

*Clear (CL)*, che forza in uscita lo stato 0 e cioè  $Q = 0$ ,  $\bar{Q} = 1$ ;

*Preset (PR)*, che forza in uscita lo stato 1 e cioè  $Q = 1$ ,  $\bar{Q} = 0$ .

Lo studio dei flip-flop è fondamentale per la comprensione della maggior parte dei circuiti sequenziali come contatori, registri, memorie, microprocessori; così come la porta NAND (NOR) è alla base dei dispositivi combinatori, allo stesso modo i flip-flop si possono considerare i *mattoni fondamentali* dell'elettronica digitale sequenziale.

I flip-flop si possono realizzare sia a porte logiche che con elementi attivi discreti (BJT e FET), ma spesso si preferisce utilizzare flip-flop già disponibili in forma integrata.

### Flip-flop Set-Reset asincrono. Latch SR

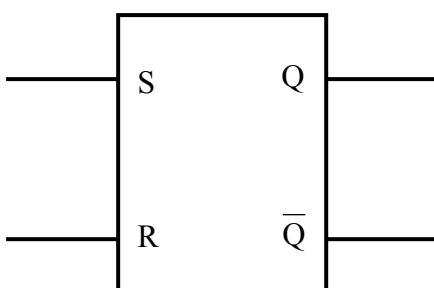

Il flip-flop Set-Reset (FF-SR) o *latch SR* (derivato dal verbo “to latch” che significa “bloccare”) è uno dei più semplici circuiti sequenziali asincroni in grado di memorizzare una informazione binaria a un bit. Esso consta di due ingressi *S* ed *R* denominati *SET* (letteralmente “porre”) e *RESET* (letteralmente “riporre”) e di un'uscita *Q*. In genere anche dell'uscita negata  $\bar{Q}$ . In figura è mostrato il simbolo logico del FF-SR insieme alla tavola della verità.

| S | R | $Q_{n+1}$ | Commento          |

|---|---|-----------|-------------------|

| 0 | 0 | $Q_n$     | Conserva lo stato |

| 0 | 1 | 0         | Memorizza 0       |

| 1 | 0 | 1         | Memorizza 1       |

| 1 | 1 | ?         | Indeterminato     |

Tabella 1

La prima riga della tabella della verità indica che la combinazione d'entrata  $S = R = 0$  lascia inalterato lo stato logico della linea  $Q$ , giacché con  $Q_n$  si è indicato lo stato presente dell'uscita e con  $Q_{n+1}$  quello che l'uscita assume dopo aver imposto i valori d'entrata  $S$  e  $R$ . In altre parole, se il flip-flop si trova nello stato  $Q_n = 0$  e si applica in entrata  $S = R = 0$  l'uscita rimane nello stesso stato cioè:  $Q_{n+1} = Q_n = 0$ ; analogamente se  $Q_n = 1$  e  $S = R = 0$  lo stato futuro coincide sempre con  $Q_n$  per cui:  $Q_{n+1} = Q_n = 1$ . Ovviamente l'uscita  $\bar{Q}$  assume il valore complementare di  $Q$  e pertanto non è stato indicata nella tabella della verità.

La seconda riga ci informa che se  $S = 0$  e  $R = 1$  (operazione di Reset) l'uscita  $Q$  si porterà nello stato  $Q_{n+1} = 0$  indipendentemente dal valore precedente 0 o 1 di  $Q_n$ .

La terza riga indica che se  $S = 1$  e  $R = 0$  (operazione di Set) l'uscita si porterà nello stato  $Q_{n+1} = 1$  sia che  $Q_n = 0$  che se  $Q_n = 1$ .

Nell'ultima combinazione  $S = R = 1$  è stato associato il simbolo  $Q_{n+1} = ?$  per indicare la presenza di uno stato indeterminato nell'uscita del flip-flop.

Infatti portare  $S$  e  $R$  ad 1 equivale a forzare l'uscita  $Q$  contemporaneamente a 1 e a 0 (operazioni di Set e Reset); ciò, evidentemente, è una incongruenza logica. Tale combinazione va, quindi, evitata.

### Latch a porte NOR

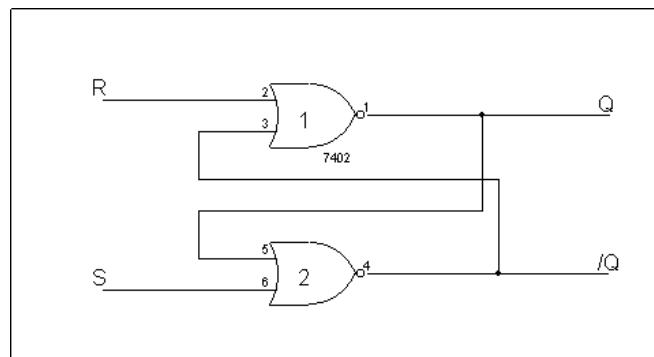

In figura si mostra lo schema a blocchi circuitale di un FF-SR realizzato con porte NOR. A seguire è riportata la tabella della verità.

| S | R | $Q_n$ | $Q_{n+1}$ | $\bar{Q}_{n+1}$ |

|---|---|-------|-----------|-----------------|

| 0 | 0 | 0     | 0         | 1               |

| 0 | 0 | 1     | 1         | 0               |

| 0 | 1 | 0     | 0         | 1               |

| 0 | 1 | 1     | 0         | 1               |

| 1 | 0 | 0     | 1         | 0               |

| 1 | 0 | 1     | 1         | 0               |

| 1 | 1 | 0     | 0         | 0               |

| 1 | 1 | 1     | 0         | 0               |

Tabella 2

Analizziamo il comportamento del circuito per le diverse combinazioni di  $S$  e  $R$  facendo riferimento alla tabella di verità riportata sopra che esprime in maniera più esplicita la dipendenza dell'uscita futura  $Q_{n+1}$  dagli ingressi  $S$  ed  $R$  e dall'uscita presente  $Q_n$ .

- 1) Se  $S = R = 0$  lo stato di uscita delle porte NOR dipende dai valori delle uscite stesse. Supponiamo che lo stato iniziale sia  $Q_n = 0$  e valutiamo quello futuro  $Q_{n+1}$ . Dal circuito si ricava che l'uscita della NOR2 vale:

$$\bar{Q}_{n+1} = \overline{S + Q_n} = \overline{0 + 0} = 1$$

Tale valore è riportato in ingresso alla NOR1, per cui:

$$Q_{n+1} = \overline{R + \bar{Q}_{n+1}} = \overline{0 + 1} = 0$$

Analogamente se fosse stato  $Q_{n+1} = 1$ :

$$\bar{Q}_{n+1} = \overline{S + Q_n} = \overline{0 + 1} = 0$$

$$Q_{n+1} = \overline{R + \bar{Q}_{n+1}} = \overline{0 + 0} = 1$$

In definitiva si sono verificate le prime due righe della tabella precedente che corrispondono sinteticamente alla prima riga della tabella 1.

L'analisi svolta mostra che per  $S = R = 0$  lo stato di uscita si conserva ma non è a priori determinato quale esso sia. Infatti nell'istante in cui si fornisce alimentazione al circuito sia  $Q$  che  $\bar{Q}$  sono inizialmente nello stato basso per cui entrambe le uscite dei NOR tendono ad 1. A causa dei ritardi di propagazione interni alle porte, però, l'uscita di uno dei due NOR va ad 1 prima dell'altro NOR in modo casuale definendo così lo stato iniziale del sistema. Se, ad esempio,  $\bar{Q} = 1$  prima di  $Q$  l'uscita del NOR1 è forzata nello stato basso; questo livello logico, riportandosi in ingresso al NOR2, conferma  $\bar{Q} = 1$  e quindi  $Q = 0$ . È possibile impostare lo stato iniziale mediante ingressi ausiliari detti di pre-assegnazione.

- 2) Se  $S = 0$  e  $R = 1$  l'uscita del NOR1 è forzata nello stato basso poiché per qualunque valore di  $Q_n$  si ha:

$$Q_{n+1} = \overline{\bar{Q}_n + R} = \bar{1} = 0$$

Tale stato è riportato in ingresso alla NOR2 la cui uscita diventa:

$$\bar{Q}_{n+1} = \overline{S + Q_n} = \overline{0 + 0} = 1$$

In definitiva si ha  $Q_{n+1} = 0$  indipendentemente dallo stato iniziale. In tal modo si sono verificate la terza e la quarta riga della tabella 2. Osserviamo che se si riportano gli ingressi nello stato di riposo  $S = R = 0$ , il valore dell'uscita  $Q = 0$  resta memorizzato nella latch.

- 3) Se  $S = 1$  e  $R = 0$  l'uscita della NOR2 è forzata nello stato basso poiché per qualunque valore di  $Q_n$  si ha:

$$\bar{Q}_{n+1} = \overline{S + Q_n} = \bar{1} = 0$$

Tale valore è riportato in ingresso alla NOR1, per cui:

$$Q_{n+1} = \overline{\bar{Q}_{n+1} + R} = \overline{0 + 0} = 1$$

Si è quindi dimostrato che per  $S = 1$  e  $R = 0$  risulta sempre  $Q_{n+1} = 1$ , come indicato nella quinta e sesta riga della tabella 2.

Se si riportano gli ingressi  $S$  ed  $R$  a zero lo stato logico di uscita  $Q = 1$  resta memorizzato.

- 4) Se  $S = R = 1$  entrambe le uscite  $Q$  e  $\bar{Q}$  sono forzate allo stato logico zero indipendentemente da quello precedente. Le uscite non sono più una il complemento dell'altra. Inoltre se si riportano gli ingressi nello stato di riposo  $S = R = 0$  può accadere:

- $S$  è riconosciuto basso prima di  $R$  per cui in ingresso si ha, anche se per un breve istante,  $S = 0$  e  $R = 1$  che rappresenta la condizione di RESET e quindi  $Q = 0$  e  $\bar{Q} = 1$ ;

- $R$  è riconosciuto basso prima di  $S$  per cui si ha la configurazione transitoria:  $S = 1$  e  $R = 0$  che rappresenta la condizione di SET che porta:  $Q = 1$  e  $\bar{Q} = 0$ .

In definitiva la combinazione  $S = R = 1$  va evitata poiché non è possibile determinare univocamente lo stato logico dell'uscita quando le entrate tornano nello stato di riposo  $S=R=0$ .

#### Tabella delle transizioni

Dalla tabella della verità del FF-SR si può costruire una mappa di Karnaugh denominata **tabella delle transizioni** nella quale sulle colonne si scrivono le diverse combinazioni delle variabili di entrata  $S$  e  $R$  e sulle righe le diverse combinazioni relative allo stato presente  $Q_n$ . In ciascuna casella si scrive il valore dello stato futuro  $Q_{n+1}$ . Si ottiene la seguente tabella:

|       |   | SR |    |    |    |

|-------|---|----|----|----|----|

|       |   | 00 | 01 | 11 | 10 |

| $Q_n$ | 0 | 0  | 0  | -  | 1  |

|       | 1 | 1  | 0  | -  | 1  |

Dalla tabella delle transizioni si perviene *all'equazione caratteristica* del flip-flop che esprime l'uscita futura  $Q_{n+1}$  in funzione di  $S$ ,  $R$  e  $Q_n$ .

Si ottiene dopo la minimizzazione:

$$Q_{n+1} = \overline{S}\overline{R} + \overline{R}Q_n$$

Allo stesso risultato si perviene anche analizzando direttamente lo schema della latch a porte NOR:

$$Q_{n+1} = \overline{\overline{R} + \overline{S} + Q_n} = \overline{R}(S + Q_n) = \overline{S}\overline{R} + \overline{R}Q_n$$

## Latch a porte NAND

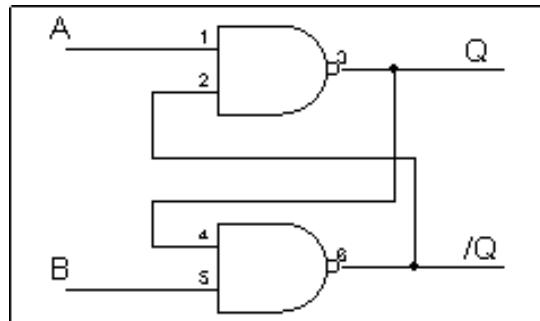

In figura è riportato lo schema elettrico di un flip-flop che utilizza porte NAND con ingressi indicati con A e B.

| A | B | $Q_{n+1}$ | Commento          |

|---|---|-----------|-------------------|

| 0 | 0 | ?         | Indeterminato     |

| 0 | 1 | 1         | Memorizza 1       |

| 1 | 0 | 0         | Memorizza 0       |

| 1 | 1 | $Q_n$     | Conserva lo stato |

Il comportamento del flip-flop, facilmente ricavabile dall'analisi del circuito, è simile a quello del flip-flop SR a porte NOR con la differenza che le linee A e B, corrispondenti agli ingressi di set e reset, sono attivi sul livello basso; in quello a porte NOR, invece, sono attivi sul livello alto. Ciò è messo in evidenza dalla tabella della verità riportata sopra che mostra come lo stato di riposo si ha per  $AB = 11$ , l'operazione di set è ottenuta portando  $A = 0$ , mentre quella di reset si ha per  $B = 0$ . Lo stato di indeterminazione si ha per:  $A = B = 0$  che forza  $Q = \bar{Q} = 1$ .

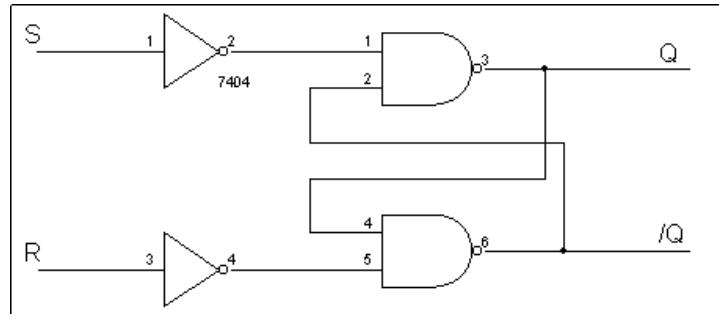

Facendo precedere gli ingressi A e B da invertitori si ottiene il circuito riportato nella figura sottostante che soddisfa la tabella della verità del flip-flop SR che è stata riportata nuovamente per comodità.

| S | R | $Q_{n+1}$ | Commento          |

|---|---|-----------|-------------------|

| 0 | 0 | $Q_n$     | Conserva lo stato |

| 0 | 1 | 0         | Memorizza 0       |

| 1 | 0 | 1         | Memorizza 1       |

| 1 | 1 | ?         | Indeterminato     |

In commercio sono disponibili latch integrate TTL e CMOS. Ricordiamo il TTL 74249 che contiene 4 latch a porte NAND; della CMOS si ricordano i quadrupli 4043 a porte NOR e il 4044 a porte NAND.

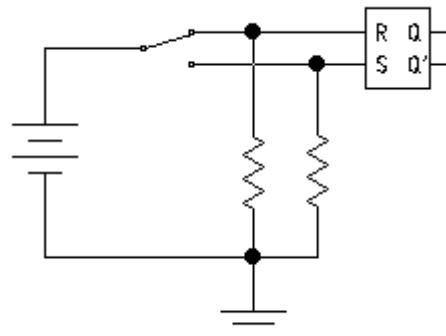

Un'interessante applicazione del latch SR si ha come *interruttore antiribalzo (anti-bounce)*. Gli interruttori meccanici, infatti, durante il loro funzionamento possono generare degli impulsi non desiderati che potrebbero modificare il comportamento di eventuali reti digitali ad essi collegati.

In realtà quando si chiude un interruttore, a causa dell'elasticità della lamina meccanica interna, non si ha una istantanea e permanente chiusura del contatto. Questo subisce un certo numero di oscillazioni prima di assumere definitivamente la posizione di interruttore chiuso.

Durante tutta la fase dei rimbalzi meccanici lo stato logico dell'uscita Q varia tra 0 e 1 un numero di volte del tutto casuale.

Si pensi, ad esempio, al contatore "elimina code" dei supermercati. Quando il salumiere preme il pulsante, il display a due cifre deve mostrare il numero successivo a quello corrente grazie alla presenza di un circuito contatore digitale. Se, però, l'interruttore non è protetto da circuito antiribalzo, alla pressione dello stesso da parte del salumiere, si generano più

impulsi che verrebbero conteggiati e quindi anziché visualizzare il numero successivo, vedremmo sui display un numero sicuramente più grande. Se, ad esempio, il display mostra il numero 30 ed alla pressione dell'interruttore si generano 5 impulsi, il successivo numero visualizzato sul display sarà 35 anziché 31.

Gli impulsi spuri si possono eliminare ponendo tra uscita e massa un condensatore di opportuna capacità (filtro passa-basso) che li cortocircuitti.

Tale tecnica produce, però, una perdita nella velocità di risposta. Nel caso di circuiti a deviatore si può usare un FF-SR come mostrato nella figura a margine, in grado di eliminare le oscillazioni in transitorio.

Quando il deviatore è nella posizione S risulta:  $SR = 10$  per cui  $Q = 1$  e  $\bar{Q} = 0$ . Quando si porta il deviatore dalla posizione S alla R, in una prima fase la lamella del deviatore non tocca i punti S e R per cui  $SR = 00$  e l'uscita conserva lo stato  $Q = 1$ . Nell'istante in cui la lamella tocca il punto R si ha:  $SR = 01$ . L'uscita diventa:  $Q = 0$  e  $\bar{Q} = 1$ . I piccoli rimbalzi meccanici fanno assumere agli ingressi SR i valori  $SR = 00$  ed  $SR = 01$  che confermano  $Q = 0$ . In definitiva l'uscita Q ha cambiato il suo stato logico, ma risulta priva di rimbalzi.

## Flip-flop SR sincronizzato

Il flip-flop SR illustrato in precedenza lavora costantemente in *modo asincrono* rispetto ai segnali di ingresso, poiché li interpreta con continuità operando in base alle combinazioni logiche da essi presentate.

Si ritiene talvolta più opportuno consentire la lettura dei segnali d'ingresso in *modo sincrono*, e cioè soltanto con il consenso di un *segnale di abilitazione*, che indichiamo con CK (clock).

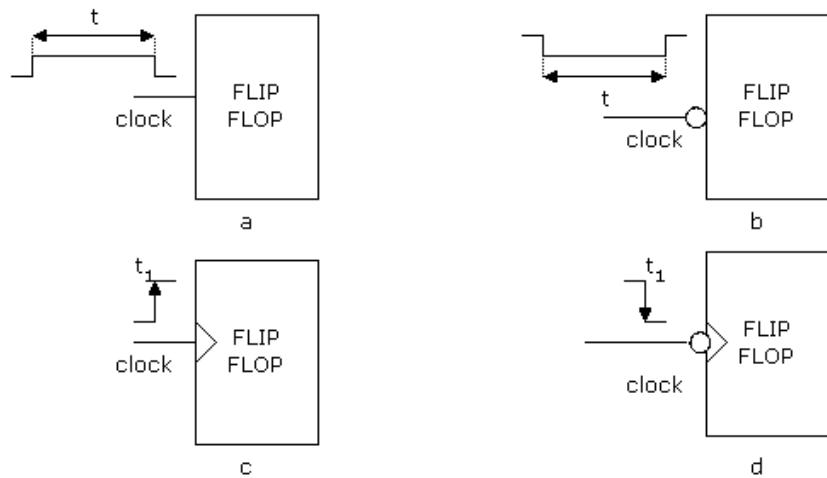

Il flip-flop si dice *attivo sui livelli* (level triggered) quando il clock è caratterizzato da un livello logico (0 o 1) applicato all'omonimo ingresso. Nelle reti sincrone attive sul livello alto si possono avere cambiamenti di stato durante tutto il tempo in cui il segnale di clock è al livello alto CK = 1.

Il flip-flop si dice *attivo su fronti* (edge triggered) quando l'eventuale modifica dello stato di uscita dipende dal *fronte positivo* o di salita (PET = Positive Edge Triggered) o dal *fronte negativo* o di discesa (NET = Negative Edge Triggered). Si dice, anche, che l'uscita si aggiorna nel:

- PET quando il clock passa da 0 a 1;

- NET quando il clock passa da 1 a 0.

Nella pratica si preferisce lavorare con reti sincrone, preferibilmente attive sui fronti, poiché risultano più affidabili e sicure nel funzionamento e, nella maggior parte dei casi, di più facile progettazione.

Nella figura sottostante si riportano i flip-flop sensibili ai livelli e i flip-flop sensibili alle transizioni. Il flip-flop "a" è sensibile al livello logico 1 e funziona nell'intervallo di tempo t. Il flip-flop "b" è sensibile al livello logico 0 durante il tempo t. Il flip-flop "c" è di tipo PET e funziona solo nell'istante  $t_1$ . Il flip-flop "d", infine, è di tipo NET e funziona solo nell'istante  $t_1$ .

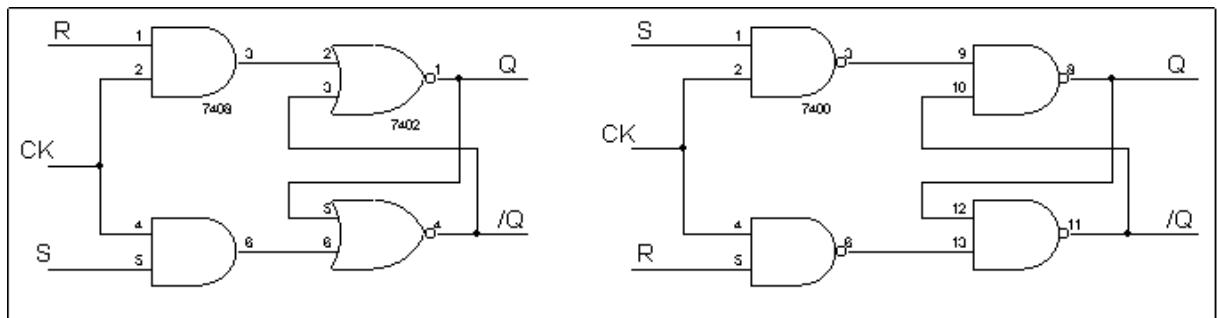

In figura si mostrano due tipici schemi di FF-SR sincronizzati

Come si vede nella figura la latch è abilitata al funzionamento solo se il segnale di clock è al livello alto:  $CK = 1$ . Quando  $CK = 0$  le uscite delle porte pilota si portano entrambe nello stato di riposo della latch, ovvero 00 per la latch a porte NOR e 11 per quella a porte NAND. Per entrambe i circuiti si perviene, con procedimento perfettamente analogo a quello seguito per le configurazioni precedenti, alla seguente tabella della verità:

| CK | S | R | $Q_n$ | $Q_{n+1}$ | $\bar{Q}_{n+1}$ | Commento                        |

|----|---|---|-------|-----------|-----------------|---------------------------------|

| 0  | X | X | 0     | 0         | 1               | Disabilitato                    |

| 0  | X | X | 1     | 1         | 0               |                                 |

| 1  | 0 | 0 | 0     | 0         | 1               | Memoria                         |

| 1  | 0 | 0 | 1     | 1         | 0               |                                 |

| 1  | 0 | 1 | 0     | 0         | 1               | Reset                           |

| 1  | 0 | 1 | 1     | 0         | 1               |                                 |

| 1  | 1 | 0 | 0     | 1         | 0               | Set                             |

| 1  | 1 | 0 | 1     | 1         | 0               |                                 |

| 1  | 1 | 1 | 0     | 1         | 1               | Indeterminata la memorizzazione |

| 1  | 1 | 1 | 1     | 1         | 1               |                                 |

Tabella 3

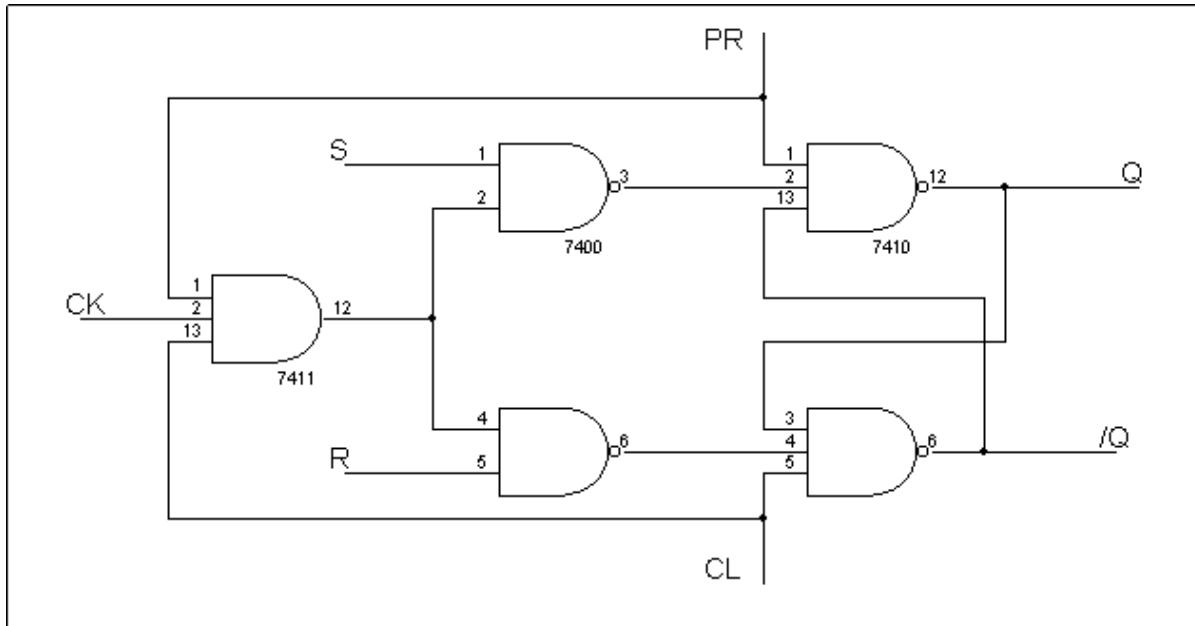

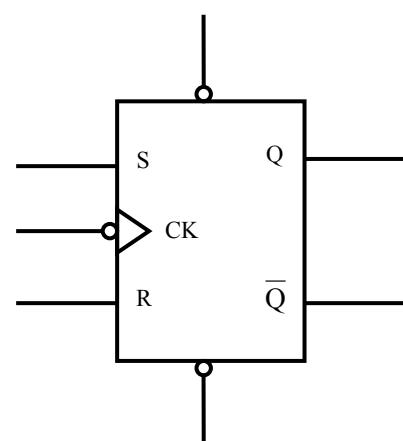

## Flip-flop SR con ingressi asincroni di preassegnazione

Nei flip-flop sincronizzati le operazioni di set ( $Q = 1$ ) o di reset ( $Q = 0$ ) si ottengono impostando opportunamente i valori degli ingressi SR e inviando, successivamente, l'impulso di sincronismo CK. In molte applicazioni è utile, invece, impostare lo stato d'uscita dei flip-flop in maniera indipendente dal valore di CK, S, R. Ciò si realizza munendo il flip-flop di ulteriori due ingressi, generalmente attivi sul livello basso, denominati PRESET (PR) e CLEAR (CL). Il primo forza l'uscita  $Q = 1$  mentre il secondo forza  $Q = 0$ . In figura si mostra lo schema di un FF-SR attivo sul livello alto di CK e munito di ingressi di preassegnazione PR e CL.

Dalla figura si deduce che gli ingressi di preassegnazione sono disattivi se  $PR = CL = 1$ ; in tal caso il flip-flop opera nel modo consueto. Se si porta  $PR = 0$  e  $CL = 1$ , il segnale di clock è inibito e con esso le porte pilota: l'uscita  $Q$  si porta ad 1. Se invece, si pone,  $CL = 0$  e  $PR = 1$ , si ottiene  $Q = 0$ . La combinazione  $CL = PR = 0$  non è ammessa poiché porta il flip-flop nello stato di indeterminazione e produce le seguenti uscite:  $Q = 1$  e  $\bar{Q} = 1$  ovviamente incongruenti. In figura si mostra la tabella di verità e il simbolo logico di un FF-SR master-slave munito di ingressi asincroni di preassegnazione. Il cerchietto su PR, CL e CK indica, come al solito, che tali linee sono attive sul livello basso.

| PR | CL | CK | S | R | $Q_{n+1}$ |

|----|----|----|---|---|-----------|

| 0  | 1  | X  | X | X | 1         |

| 1  | 0  | X  | X | X | 0         |

| 1  | 1  | 0  | X | X | $Q_n$     |

| 1  | 1  | 1  | X | X | $Q_n$     |

| 1  | 1  | □  | 0 | 0 | $Q_n$     |

| 1  | 1  | □  | 0 | 1 | 0         |

| 1  | 1  | □  | 1 | 0 | 1         |

| 1  | 1  | □  | 1 | 1 | ?         |

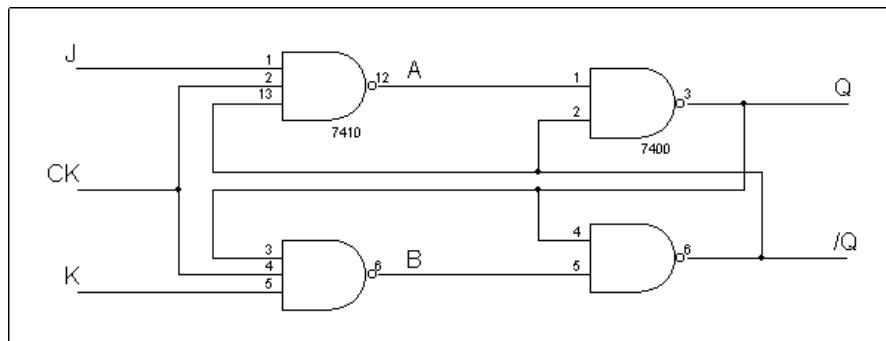

## Flip-flop JK

Il flip-flop JK è un dispositivo con due entrate di comando J e K che operano in modo analogo alle entrate SR di un flip-flop set-reset con la differenza che se:  $J = K = 1$ , l'uscita Q cambia stato. In tal modo viene eliminata l'indeterminazione che si ha in un SR quando si pone  $S = R = 1$ . Nella figura si mostra lo schema base del FF-JK insieme alla tabella della verità.

| CK | J | K | $Q_{n+1}$   |

|----|---|---|-------------|

| 0  | X | X | $Q_n$       |

| 1  | 0 | 0 | $Q_n$       |

| 1  | 0 | 1 | 0           |

| 1  | 1 | 0 | 1           |

| 1  | 1 | 1 | $\bar{Q}_n$ |

Le prime quattro righe della tabella della verità coincidono con quelle di un FF-SR avente  $S = J$  e  $R = K$ , come è facile verificare dall'analisi del circuito. L'ultima riga della tabella indica che per  $J = K = 1$  l'uscita cambia stato.

Infatti supponiamo che lo stato presente sia  $Q = 0$  e  $J = K = 1$ . Quando CK diventa 1 le uscite delle porte pilota si portano nello stato:  $A = 0$  e  $B = 1$  l'uscita Q è forzata nello stato  $Q=1$  e di conseguenza  $\bar{Q}$  diventa 0 e ciò verifica il cambio di stato dell'uscita del flip-flop.

Analogamente si può verificare che se lo stato presente è  $Q = 1$  lo stato successivo vale 0. In realtà se la durata dell'impulso CK è superiore alla somma tra il tempo di propagazione di una porta pilota con quella di una porta della latch finale, l'uscita Q commuta più di una volta per cui non è determinato l'effettivo stato finale di uscita del flip-flop quando CK torna a zero. Ne risulta un funzionamento instabile, di tipo oscillatorio, il cui periodo è il doppio del tempo di risposta del dispositivo; tale fenomeno è noto come *corsa critica*.

Per superare tale inconveniente si deve rendere la durata  $T_{CK}$  dell'impulso di clock minore di due tempi di ritardo di propagazione.

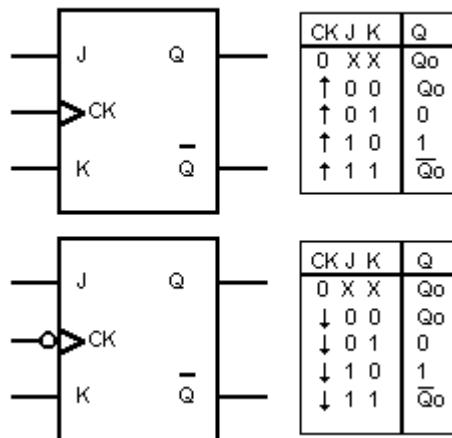

In tal modo si ottengono i flip-flop JK *edge triggered* di tipo PET, attivo sul fronte di salita di CK, o NET, attivo su quello di discesa. In figura si mostrano i simboli logici di un FF-JK tipo PET e NET insieme alle tabelle di verità.

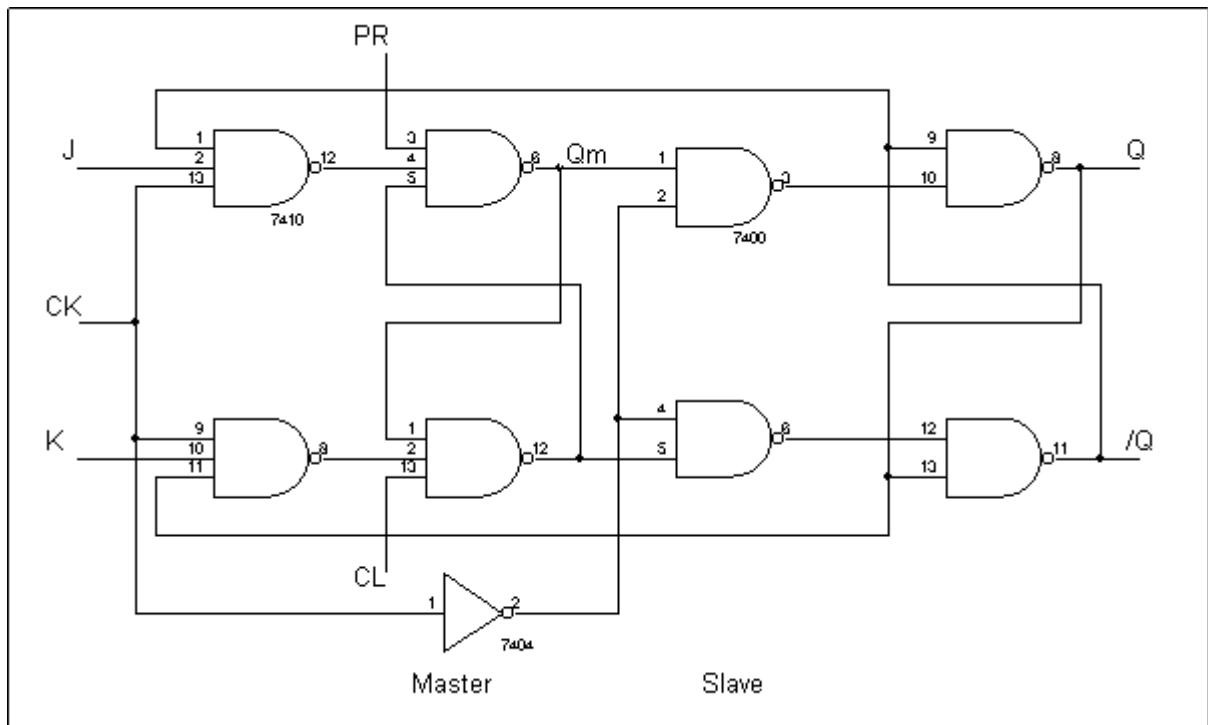

La corsa critica può essere evitata mediante la struttura master-slave di figura.

Il master-slave è costituito da due flip-flop SR posti in cascata; è inoltre presente una retroazione tra le due uscite  $Q$  e  $\bar{Q}$  e gli ingressi  $J$  e  $K$  tramite le porte NAND poste in entrata. Analizziamo il funzionamento del dispositivo per  $J = K = 1$ . Supponiamo che inizialmente ed in assenza di segnale di clock, sia  $Q_m = Q = 0$ . Quando  $CK$  diventa 1 il master è abilitato al funzionamento mentre lo slave è bloccato ( $\bar{CK} = 0$ ); gli ingressi di comando del master diventano:

$$S = J \cdot \bar{O} = 1$$

$$R = K \cdot O = 0$$

ciò corrisponde ad un'operazione di set, per cui

$$Q_m = 1 \ ; \ \bar{Q}_m = 0$$

Tale situazione si conserva per tutto il tempo in cui  $CK = 1$ . Quando  $CK$  torna a 0 lo slave viene abilitato e il master bloccato. Gli ingressi di comando dello slave valgono, ora:

$$S = Q_m = 1$$

$$R = \bar{Q}_m = 0$$

Ciò corrisponde ad una operazione di set per lo slave le cui uscite diventano:

$$Q = 1 \ ; \ \bar{Q} = 0$$

I nuovi valori d'uscita si riportano in entrata, ma il master è bloccato ( $CK=0$ ), interrompendo l'anello di reazione e, con esso, la corsa critica. In definitiva si è avuto un cambiamento dello stato di uscita senza corsa critica.

Il comportamento complessivo del master-slave è assimilabile a un NET se si suppone che gli ingressi JK restino inalterati per l'intera durata dell'impulso di clock. Per tale motivo il simbolo logico del master-slave è uguale a quello di un FF NET.

#### Tabella delle transizioni

È una mappa di Karnaugh che esprime la relazione tra le entrate JK e lo stato presente  $Q_n$ . In ogni casella si scrive il valore assunto dallo stato futuro  $Q_{n+1}$  per la particolare combinazione tra J, K e  $Q_n$ . In figura si mostra tale tabella insieme a quella della verità. In quest'ultima si è omesso il segnale di clock in modo da prescindere dal tipo di flip-flop (NET, PET, o Master-Slave).

|       |   | JK |    |    |    |

|-------|---|----|----|----|----|

|       |   | 00 | 01 | 11 | 10 |

| $Q_n$ | 0 | 0  | 0  | 1  | 1  |

|       | 1 | 1  | 0  | 0  | 1  |

| J | K | $Q_{n+1}$   |

|---|---|-------------|

| X | X | $Q_n$       |

| 0 | 0 | $Q_n$       |

| 0 | 1 | 0           |

| 1 | 0 | 1           |

| 1 | 1 | $\bar{Q}_n$ |

Dalla tabella delle transizioni si ricava, per minimizzazione, l'equazione caratteristica. Raggruppando le due coppie di 1 adiacenti per riga si ha:

$$Q_{n+1} = J\bar{Q}_n + \bar{K}Q_n$$

## Flip-flop D (Dato)

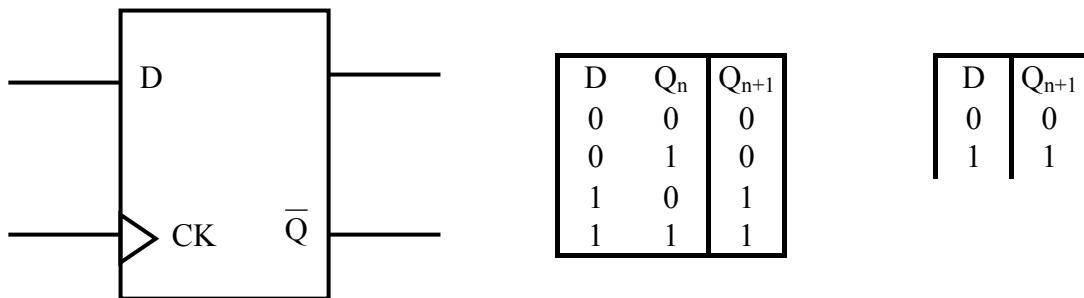

È un flip-flop avente una sola entrata denominata D (Dato) e due uscite complementari Q e  $\bar{Q}$ . L'uscita Q assume lo stesso stato logico dell'ingresso D dopo che si è applicato il segnale di sincronismo CK. In figura si mostra il simbolo logico e la tabella della verità.

Dalla tabella della verità si ricava la tabella delle transizioni.

|                |   | D |   |

|----------------|---|---|---|

|                |   | 0 | 1 |

| Q <sub>n</sub> | 0 | 0 | 1 |

|                | 1 | 0 | 1 |

L'equazione caratteristica si determina dalla tabella della verità o da quella delle transizioni. Si ha:

$$Q_{n+1} = D$$

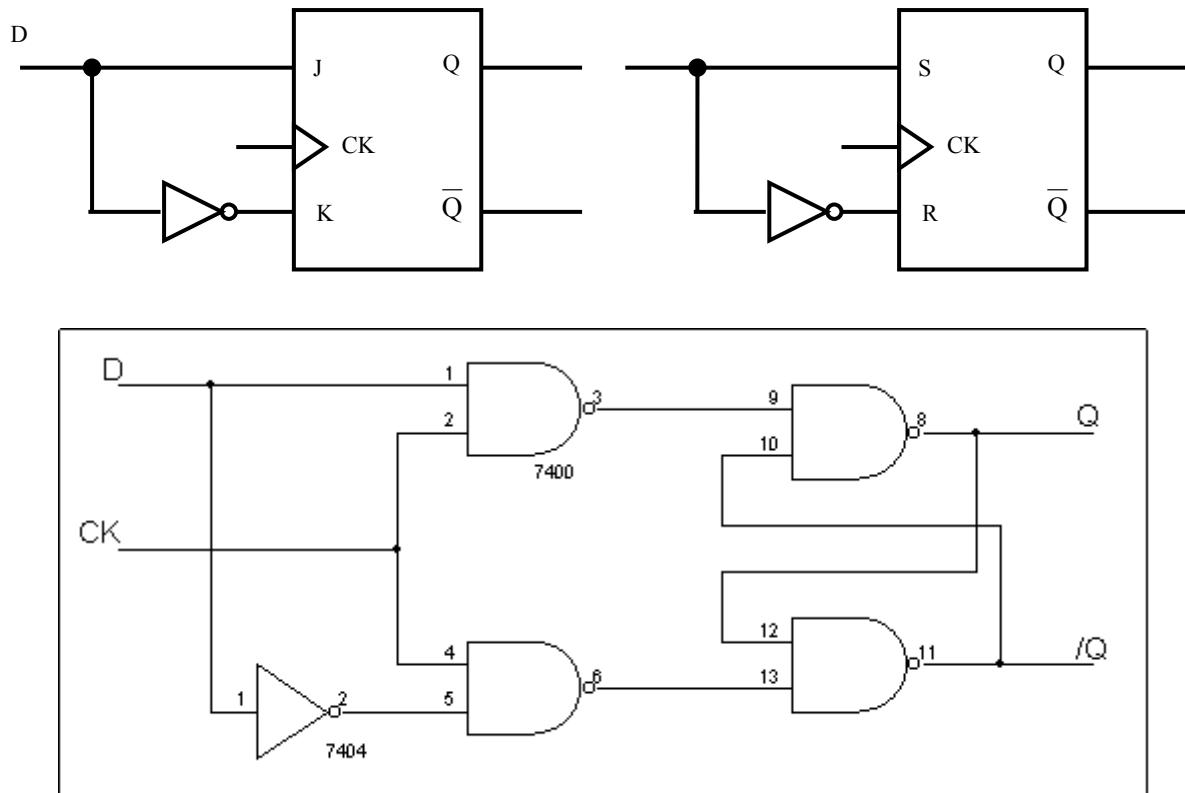

Un flip-flop D si può realizzare utilizzando un flip-flop JK. L'equazione caratteristica del JK è stata ricavata in precedenza e vale:

$$Q_{n+1} = J\bar{Q}_n + \bar{K}Q_n$$

L'equazione caratteristica del flip-flop D si può così riscrivere:

$$Q_{n+1} = D(\bar{Q}_n + Q_n) = D\bar{Q}_n + DQ_n$$

Confrontando l'ultimo risultato con l'equazione caratteristica del JK si ricava:

$$J = D \quad e \quad \bar{K} = D$$

ovvero

$$J = D \quad e \quad K = \bar{D}$$

Il flip-flop D è quindi un caso particolare di JK in cui si utilizzano solo la seconda e la terza riga della tabella della verità.

Poiché per tali combinazioni delle variabili di ingresso un flip-flop JK equivale ad un SR, si deduce che un flip-flop D si può ricavare anche da un SR ponendo  $S = D$  e  $R = \bar{D}$ .

In figura si mostrano le relative soluzioni circuitali.

I flip-flop D sono disponibili con diversi schemi logici atti a rendere il dispositivo attivo sul fronte di salita del clock (PET) o su quello di discesa (NET) o con struttura master-slave. Anche per i flip-flop D si possono implementare le reti di preassegnazione di preset e clear simili a quelle esaminate per il flip-flop SR.

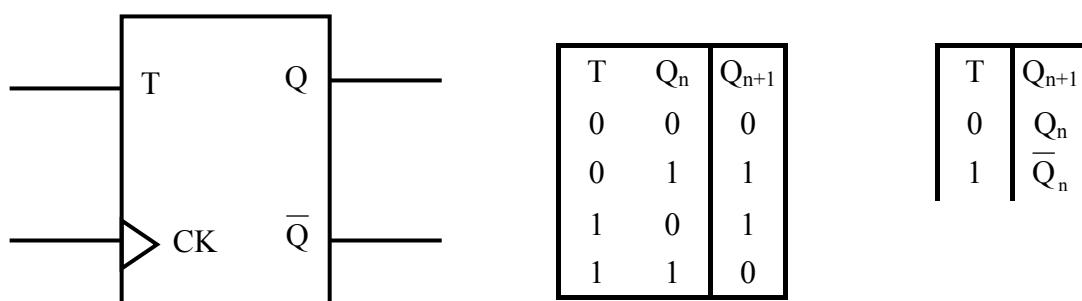

### Flip-flop T (Toggle)

È un flip-flop con ingresso T e due uscite Q e  $\bar{Q}$ . Se  $T = 1$  le uscite cambiano stato ad ogni impulso di clock mentre se  $T = 0$  lo uscite conservano lo stato logico precedente. In figura si riporta il simbolo logico e la tabella della verità.

Dalla tabella della verità si ricava la tabella delle transizioni

|       |   |   |

|-------|---|---|

|       | T |   |

| $Q_n$ | 0 | 1 |

| 0     | 0 | 1 |

| 1     | 1 | 0 |

L'equazione caratteristica risulta:

$$Q_{n+1} = T\bar{Q}_n + \bar{T}Q_n = T \oplus Q_n$$

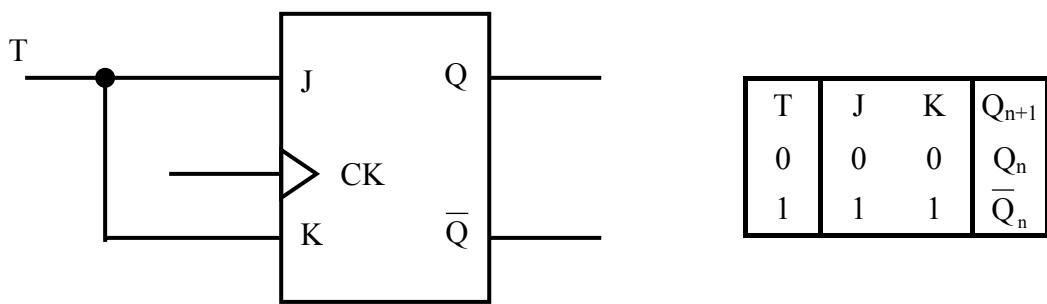

Se si tiene conto che l'equazione caratteristica di un flip-flop JK è:

$$Q_{n+1} = J\bar{Q}_n + \bar{K}Q_n$$

si ricava immediatamente, per confronto delle due equazioni caratteristiche:

$$J = K = T$$

Un flip-flop T, pertanto, si può realizzare utilizzando un flip-flop JK collegando insieme J con K. In figura si mostra la soluzione circuitale insieme alla tabella della verità.

## Produzione commerciale

In commercio sono disponibili numerosi circuiti integrati contenenti tipicamente, uno, due, o quattro flip-flop attivi sul livello o sulle transizioni del segnale di clock spesso forniti di ingressi asincroni di Preset e Clear o semplicemente del solo Clear.

L'integrato TTL 7474 contiene due flip-flop D indipendenti di tipo PET muniti di Preset e Clear. Le caratteristiche elettriche generali dei flip-flop TTL dipendono dalla serie di appartenenza e sono riportate in modo dettagliato sui manuali tecnici. In particolare, per la serie standard, la massima frequenza del segnale di clock è tipicamente intorno ai 30 MHz mentre la potenza massima dissipata per ogni flip-flop è di circa 50 mW.

Per quanto concerne i flip-flop della famiglia CMOS, oltre a quelli della serie 74C, compatibili nella piedinatura con i corrispondenti della serie TTL, esistono numerosi tipi della serie 4000.

Il 40174 contiene sei flip-flop D di tipo PET muniti di clear e tutti comandati dallo stesso segnale di clock.

## Applicazioni dei flip-flop

I flip-flop trovano applicazione in tutti i circuiti digitali sequenziali, cioè in quei circuiti in cui le uscite, oltre a dipendere dagli ingressi esterni, dipendono anche dallo stato interno assunto in precedenza. In altre parole trova applicazione in tutti i dispositivi di memoria:

contatori, centralina dei cancelli automatici, ascensori, lavatrici, antifurto, generatori di sequenze binarie e, in particolare, in tutte le applicazioni di automazione industriale.

Questa presentazione si conclude con la proposta di un ulteriore esempio di applicazione dei flip-flop, in aggiunta al circuito antirimbalo discusso precedentemente.

### Comandi separati di marcia e di arresto

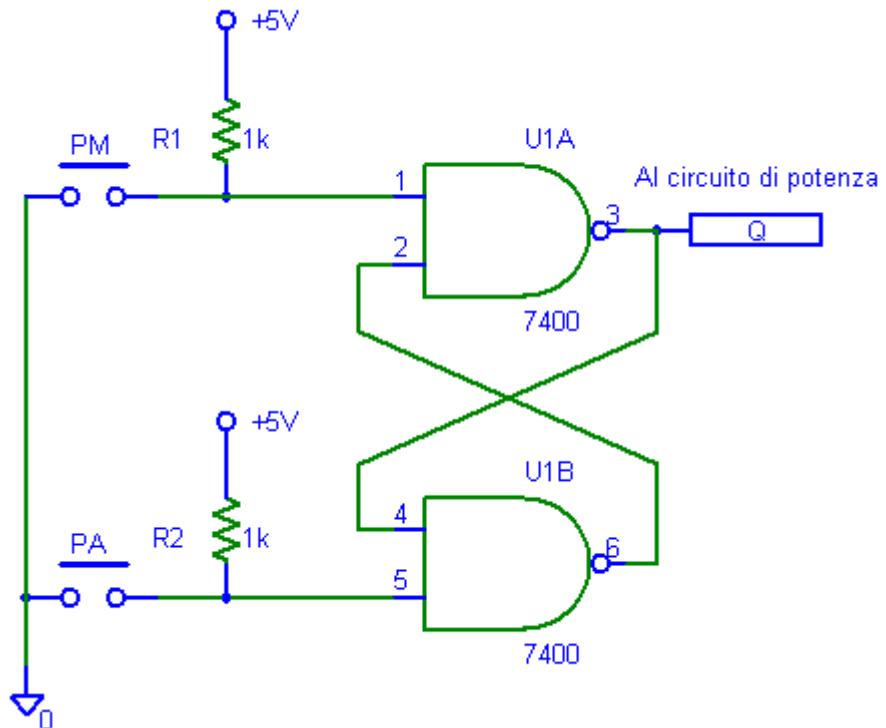

Nella figura sottostante si riporta un flip-flop SR con ingressi in logica negativa realizzato con due porte NAND comandato da due pulsanti, normalmente aperti, indicati con PM e PA. Il circuito consente i comandi separati per la marcia e l'arresto di apparati di potenza.

Quando i pulsanti sono nello stato di riposo, gli ingressi del flip-flop sono al livello logico alto: l'uscita conserva lo stato precedente.

Per mettere in marcia il circuito di potenza, ovvero porre  $Q = 1$ , si deve pigiare il pulsante di marcia PM. Ciò provoca il collegamento a massa del pin 1 e quindi l'uscita Q si porta al livello logico alto: il circuito di potenza viene attivato.

Rilasciando il pulsante l'uscita conserva lo stato  $Q = 1$  e l'impianto rimane in marcia. Per arrestare l'impianto si deve pigiare il pulsante di arresto PA. Ciò provoca il collegamento a massa del piedino 5 e quindi  $Q = 0$ .

L'impianto si arresta. Rilasciando il pulsante l'uscita conserva lo stato  $Q = 0$  e l'impianto rimane nello stato di arresto.

Flip-flop SR per la marcia e l'arresto di apparati.